# RAJ240090 / RAJ240100

3 to 10 Series Li-ion Battery Manager

### 1.1 Features

- Fully integrated battery management solution with battery capacity measurement and programmable protection capability.

- Supports up to 10 Li-ion or Li-Polymer battery cells in series. RAJ240090 supports 3 to 8 series cells, RAJ240100 supports 3 to 10 series cells.

- Integrated with Renesas Ultra Low Power RL78 CPU core for multi-function process

- Memory

Code flash memory: 128KB Data flash memory (up to 100,000 erase/write cycles): 4 KB SRAM: 7KB

#### Clock generator

High speed on-chip oscillator: up to 32 MHz Low speed on-chip oscillator: 32 KHz AFE high speed on-chip oscillator: 4.194 MHz AFE low speed on-chip oscillator: 131.072 KHz

#### General Purpose I/O Ports

Total: 31 pins CMOS input/output: 20 CMOS input: 4 N-ch open drain Input/output [6V tolerance]: 4 High voltage input/output [VCC tolerance]: 3

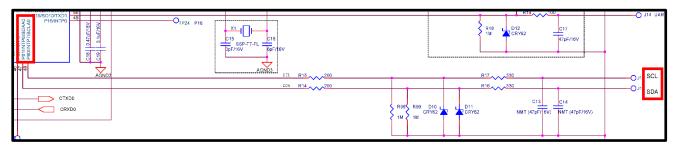

#### Serial interface

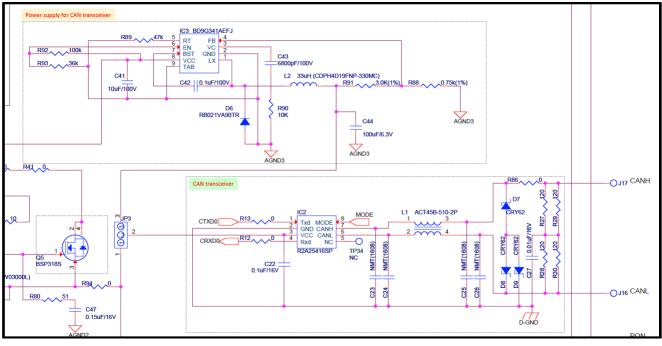

CSI (SPI): 2 channels I2C: 1 channel UART: 2 channels Simplified I2C: 2 channels CAN interface (RS-CAN lite): 1 channel

#### Timer

MCU 16-bit timer: 6 channels MCU 12-bit interval timer: 1 channel

MCU Real time clock: 1 channel

- AFE timer: 2 channels

- AFE timer A: setting range: 125 ms to 64 s

- AFE timer B: setting range : 30.52 us to 125 ms

# 1.2 Applications

- E-Bike, E-Scooter, Pedal-Assist Bicycle

- Power Tool, Vacuum Cleaner, Drone

- Battery Backup System, Energy Storage System (ESS)

### 1.3 Description

R01DS0301EJ0201 Rev.2.01 Jun. 7, 2018

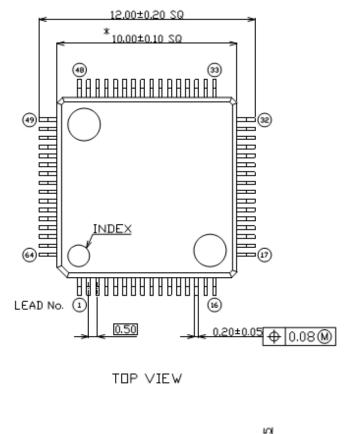

Embedded A/D converter AFE 15-bit resolution sigma-delta A/D converter MCU 8/10-bit resolution A/D converter <R> ■ Battery cell voltage and temperature (AN port voltage) detection circuit Monitoring over/under voltage and temperature by Sigmadelta AD converter (AFE) without controlling from MCU Current integration circuit 18-bit resolution sigma-delta A/D converter Impedance measurement circuit Simultaneous measurement of battery voltage and current Over current detection circuit Short circuit current detection Charge overcurrent detection Discharge overcurrent detection Charge wakeup current detection Discharge wakeup current detection Series regulator 3.3V or 5.0V CREG2 Over 100mA output current by external Nch MOSFET Charge and Discharge MOSFET control High side Nch MOSFET drive circuit embedded Programmable MOSFET control by 8-bit PWM Support RTC function To connect External crystal resonator (32.768 kHz) and generate internal clock. <R> Voltage and temperature condition Power supply voltage: VCC = 4.0 to 50 V Operating ambient temperature RAJ240090 supports  $T_A = -20$  to  $+85^{\circ}C$ RAJ240100 supports  $T_A = -40$  to  $+85^{\circ}C$ Package Information 64 pin plastic mold LQFP ([Body] 10.0 mm x 10.0 mm, 0.5 mm pitch)

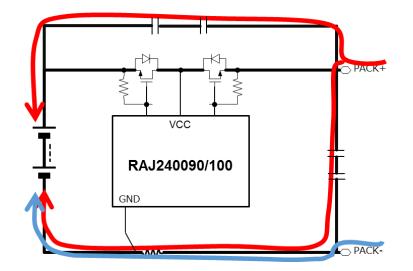

RAJ240090 / RAJ240100 are Renesas Li-ion battery fuel gauge IC (FGIC) which consist of a MCU device and an AFE device in a single package. Pack with a variety of battery management features and Renesas RL78 CPU core which has multiple low power modes and capable of achieving high performance in ultra-low power operation. RAJ240090 / RAJ240100 fuel gauge IC have control firmware stored in embedded flash memory to control attached embedded analog and digital circuits to execute battery voltage / current / temperature measurement, remaining capacity estimation, over current / voltage / temperature protection and other battery management operations.

# **Table of Contents**

| 1.           | Introduction                                           | 1  |

|--------------|--------------------------------------------------------|----|

| 1.1          | Features                                               | 1  |

| 1.2          | Applications                                           | 1  |

| 1.3          | Description                                            | 1  |

| 2.           | OUTLINE                                                | 1  |

| 2.1          | Outline of Functions                                   | 1  |

| 2.2          | RAJ240090 Pin Configuration                            | 3  |

| 2.3          | RAJ240100 Pin Configuration                            | 4  |

| 3.           | PIN FUNCTIONS                                          | 5  |

| 3.1          | Pin identification                                     | 5  |

| 3.2          | Pin Functions                                          | 7  |

| 3.3          | Pin Block Diagram                                      | 10 |

| 4.           | ELECTRICAL SPECIFICATIONS                              | 22 |

| 4.1          | Absolute Maximum Ratings                               | 22 |

| 4.2          | Power supply voltage condition                         | 24 |

| 4.3          | Supply current characteristics                         | 24 |

| 4.4          | Oscillator Characteristics                             | 25 |

| 4.5          | Pin characteristics                                    | 26 |

| 4.6          | AC Characteristics                                     | 31 |

| 4.7          | MCU peripheral circuit characteristics                 | 35 |

| 4.8          | AFE peripheral circuit characteristics                 | 51 |

| 4.9          | RAM Data Retention Characteristics                     | 58 |

| 4.10         | ) Flash Memory Programming Characteristics             | 58 |

| 4.1 <i>°</i> | Dedicated Flash Memory Programmer Communication (UART) | 58 |

| 4.12         | 2 Timing of Entry to Flash Memory Programming Modes    | 59 |

| 5.           | Detailed description                                   | 60 |

| 5.1          | Overview                                               | 60 |

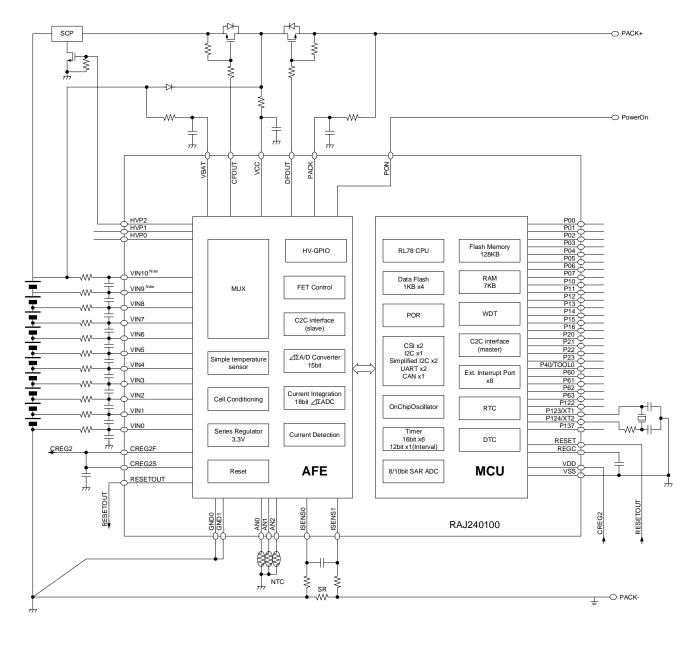

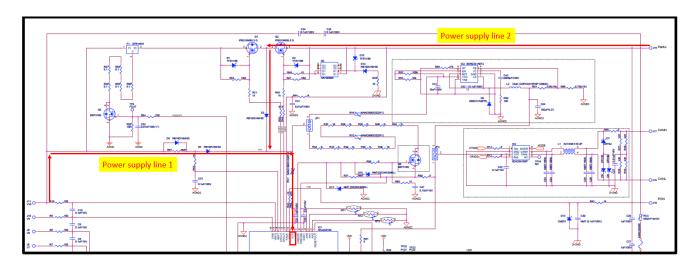

| 5.2          | System block diagram                                   | 60 |

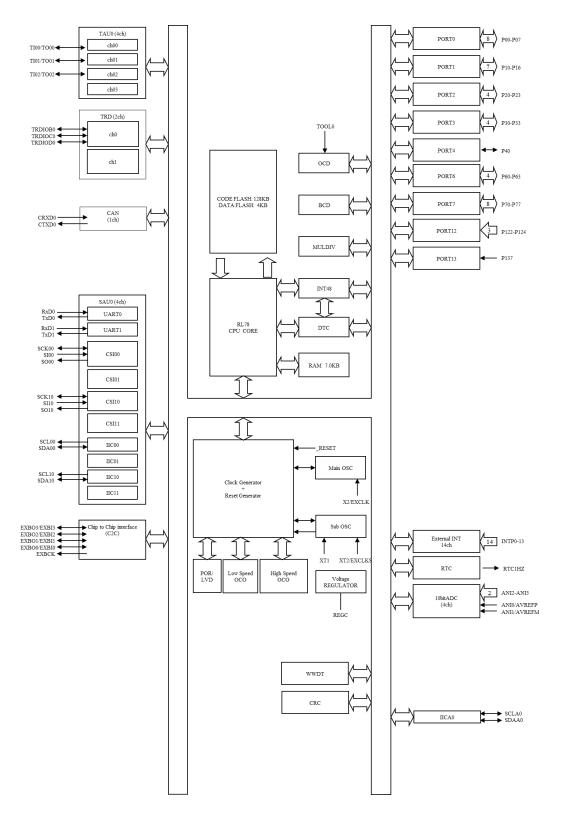

| 5.3          | MCU block diagram                                      | 61 |

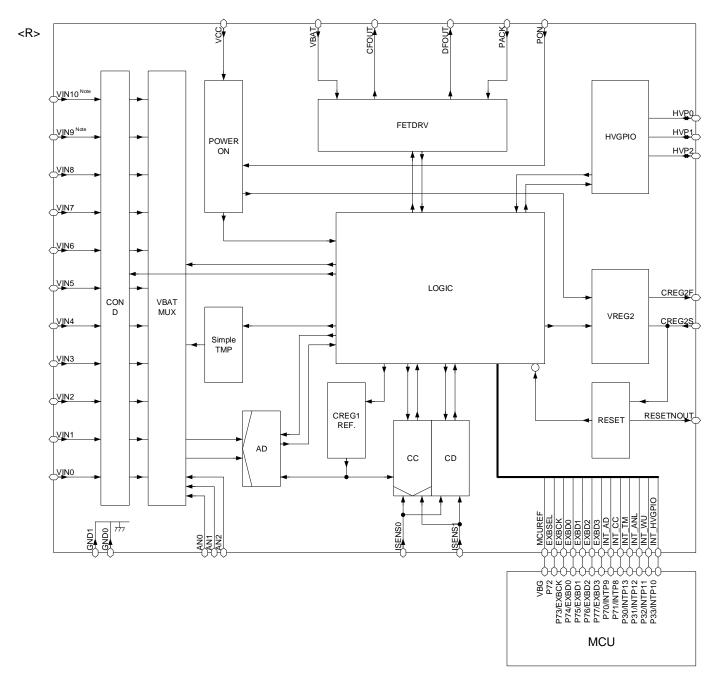

| 5.4          | AFE block diagram                                      | 62 |

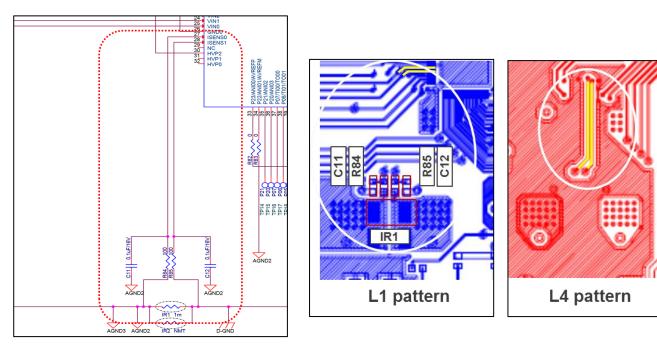

| 6.           | Application Guideline                                  | 63 |

| 6.1          | Typical Application Specification                      | 63 |

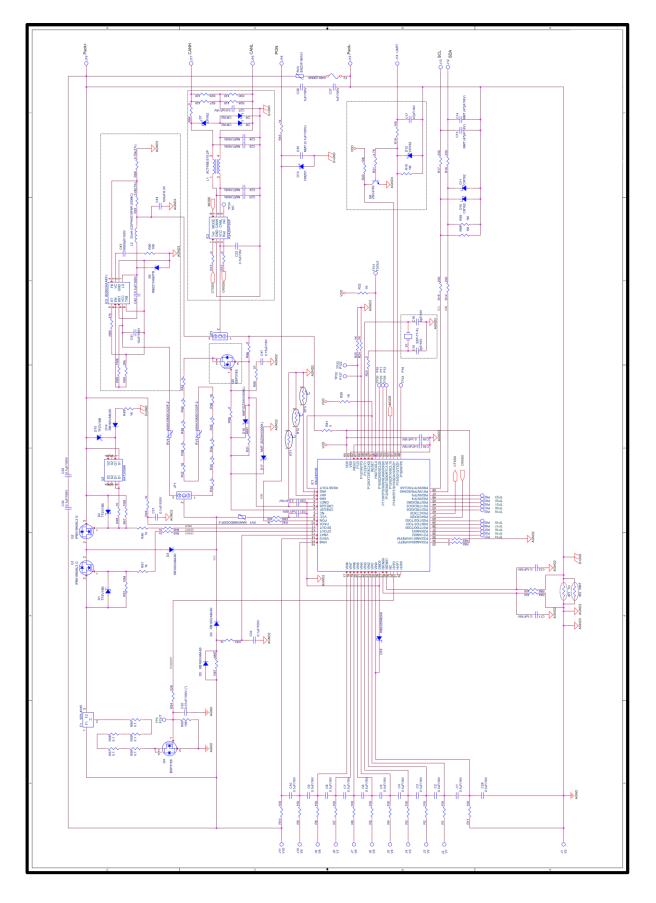

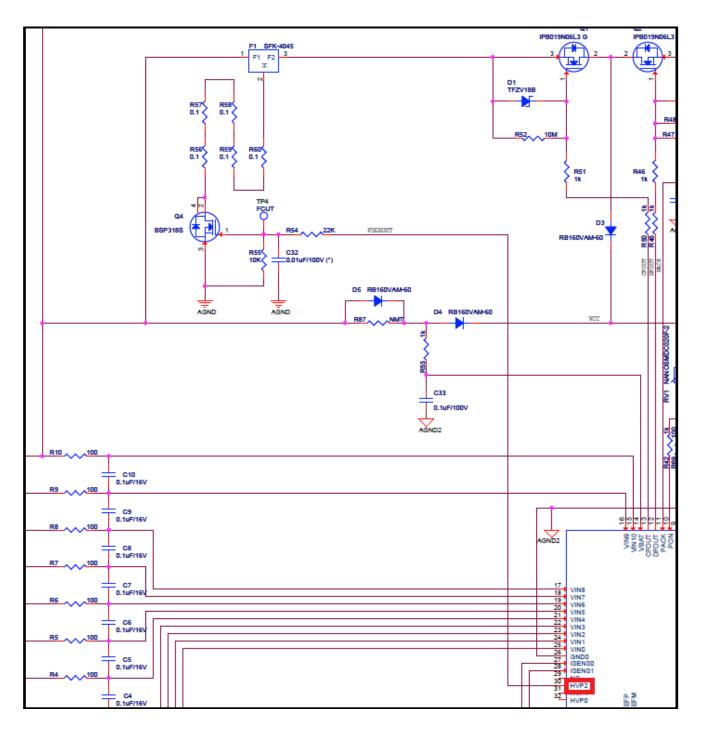

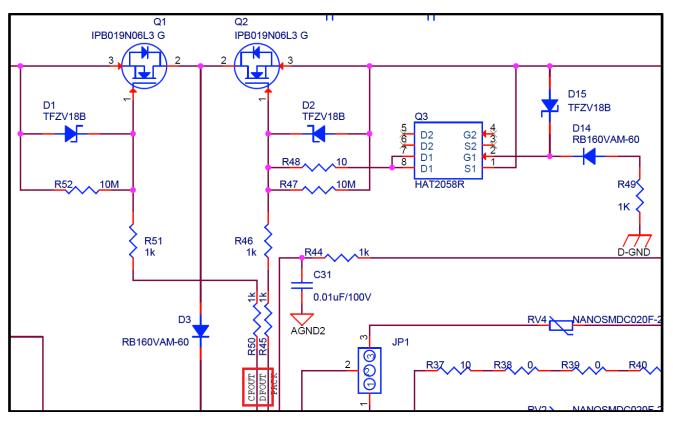

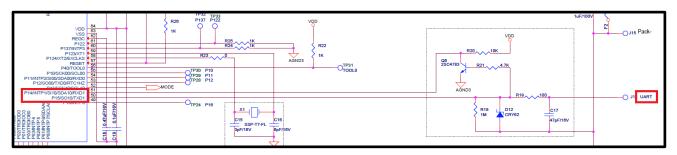

| 6.2          | Typical Application Circuit                            | 64 |

| 6.3          | Circuit Design Guideline                               | 65 |

| 6.4          | Layout Guidelines                                      | 75 |

| 7.           | PACKAGE DRAWINGS                                       | 80 |

| REVIS        | SION HISTORY                                           | 81 |

# 2. OUTLINE

### 2.1 Outline of Functions

Caution This outline describes the functions at the time when Peripheral I/O redirection register 0 (PIOR0) is set to "00H".

|                        | Item                        | Description                                                                       |   |  |  |

|------------------------|-----------------------------|-----------------------------------------------------------------------------------|---|--|--|

| Code flas              | h memory                    | 128 KB                                                                            |   |  |  |

| Data Flash memory      |                             | 4 KB                                                                              |   |  |  |

| RAM                    |                             | 7 KB                                                                              |   |  |  |

| Address s              | size                        | 1MB                                                                               |   |  |  |

| Main syste             | em clock High speed on-chip | HS (high-speed main) mode: 1 to 32 MHz                                            | - |  |  |

|                        | Oscillator clock(fIH)       | LS (low-speed main) mode: 1 to 8 MHz ,                                            |   |  |  |

| Subsyster              | m clock                     | XT1 (crystal) oscillation, external subsystem clock input (EXCLKS) 32.768 kHz     |   |  |  |

| Low spee               | d on-chip oscillator clock  | 15 kHz (TYP.)                                                                     |   |  |  |

| General p              | ourpose register            | 8 bits x 32 registers (8 bits x 8 registers x 4 banks)                            |   |  |  |

| Minimum                | instruction execution time  | 0.03125 us(Internal high speed oscillation clock: fIH = 32 MHz)                   |   |  |  |

|                        |                             | 30.5 us (Subsystem clock : f <sub>SUB</sub> = 32.768 kHz operation)               |   |  |  |

| Instruction            | n set                       | Data transmission (8/16 bits)                                                     |   |  |  |

|                        |                             | Addition and subtraction/logical operations (8/16 bits)                           |   |  |  |

|                        |                             | Multiplication (8×8 bits,16×16 bits),Division (16÷16 bits,32÷32 bits)             |   |  |  |

|                        |                             | Multiplication and Accumulation (16 bits × 16 bits + 32 bits)                     |   |  |  |

|                        |                             | Rotate, barrel shift, bit manipulation (set, reset, test, Boolean operation) etc. |   |  |  |

| I/O Port               | CMOS I/O                    | 20                                                                                |   |  |  |

|                        | CMOS input                  | 4                                                                                 |   |  |  |

|                        | N-ch open-drain I/O         | 4                                                                                 |   |  |  |

|                        | [6V tolerance)              |                                                                                   |   |  |  |

|                        | High voltage I/O            | 3                                                                                 |   |  |  |

| Timer                  | 16-bit timer                | 6 channels                                                                        |   |  |  |

|                        |                             | (TAU : 4 channels, Timer RD : 2 channels)                                         |   |  |  |

|                        | Watchdog timer              | 1 channel                                                                         |   |  |  |

|                        | Real time clock             | 1 channel                                                                         |   |  |  |

|                        | 12-bit interval timer       | 1 channel                                                                         |   |  |  |

|                        | Timer output                | Timer outputs: 6 channels                                                         |   |  |  |

|                        |                             | PWM outputs: 3 channels                                                           |   |  |  |

|                        | RTC output                  | 1 channel                                                                         |   |  |  |

| 8/10-bit re            | esolution A/D converter     | 4 channels                                                                        |   |  |  |

| Serial inte            | erface                      | • CSI: 1 channel/UART: 1 channel/simplified I2C: 1 channel                        |   |  |  |

|                        |                             | CSI: 1 channel/UART: 1 channel/simplified I2C: 1 channel                          |   |  |  |

|                        | I <sup>2</sup> C bus        | 1 channel                                                                         |   |  |  |

|                        | Can interface (RS-CAN lite) | 1 channel                                                                         |   |  |  |

| Vector                 | Internal                    | 22                                                                                |   |  |  |

| interrupt              | External                    | 15 (6 sources is connected to AFE in the chip)                                    |   |  |  |

| source                 |                             | · · · · · · · · · · · · · · · · · · ·                                             |   |  |  |

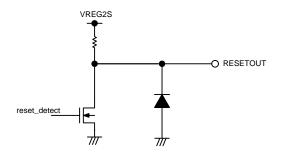

| Reset                  |                             | Reset by RESET pin (reset circuit output of AFE connected to RESETOUT)            |   |  |  |

|                        |                             | Internal reset by watchdog timer                                                  |   |  |  |

|                        |                             | Internal reset by illegal instruction execution Note                              |   |  |  |

|                        |                             | internal reset by RAM parity error                                                |   |  |  |

|                        |                             | internal reset by illegal memory access                                           |   |  |  |

| Dn-chip debug function |                             | Support                                                                           |   |  |  |

**Note** The illegal instruction execution is generated when instruction code FFH is executed. Reset by the illegal instruction execution not is issued by emulation with the in-circuit emulator or on-chip debug emulator.

| Item                                                  | Description                                                                                 |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------|

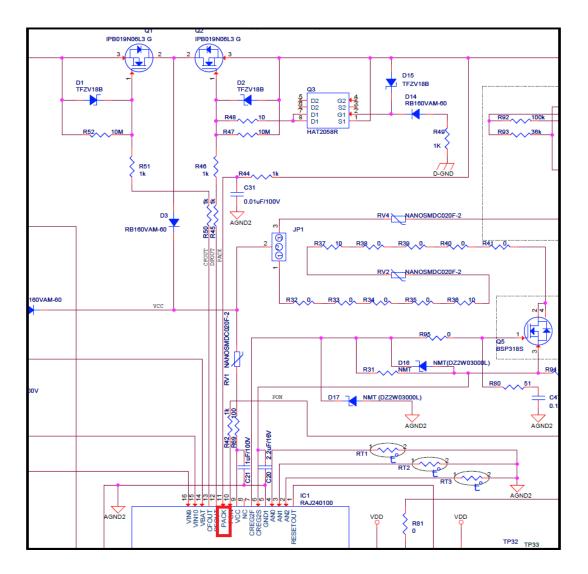

| PWM                                                   | 8 bits or 10 bits ×1 for FET control                                                        |

| Sigma-delta A/D converter                             | 15-bit resolution (sigma-delta method)                                                      |

|                                                       | Battery Cell voltage (Cell 1 to 8 in RAJ240090, Cell 1 to 10 in RAJ240100)                  |

|                                                       | Battery Cell total voltage (VIN8 pin in RAJ240090, VIN10 pin in RAJ240100)                  |

|                                                       | Charge voltage (PACK pin)                                                                   |

|                                                       | PON pin input voltage                                                                       |

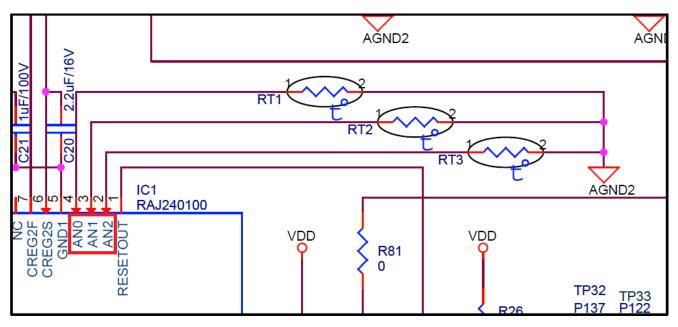

|                                                       | <ul> <li>Thermistor sensor port with on-chip pull-up 10kohm resistor: 3 channels</li> </ul> |

|                                                       | <ul> <li>On-chip simple temperature sensor (temperature range: -20 to 85C)</li> </ul>       |

|                                                       | Internal reference and supply voltage (MCU and AFE)                                         |

| Battery cell voltage and temperature (AN              | Battery Cell voltage detection                                                              |

| port voltage) detection circuit Note1                 | Over voltage (Overcharge voltage)                                                           |

|                                                       | Under voltage (Overdischarge voltage)                                                       |

|                                                       | Temperature (AN port voltage) detection                                                     |

|                                                       | Over temperature                                                                            |

|                                                       | Under temperature                                                                           |

| Current integrating circuit                           | 1 channel:18-bit resolution                                                                 |

| Current integrating circuit for impedance measurement | 1 channel:15-bit resolution                                                                 |

| Overcurrent detection circuit and wake up             | Discharge short-circuit current detection                                                   |

| current detection circuit                             | Discharge overcurrent detection                                                             |

|                                                       | Charge overcurrent detection,                                                               |

|                                                       | Wake up current detection (discharge and charge)                                            |

| Simple temperature sensor                             | 1 channel                                                                                   |

| Charge/Discharge FET control circuit                  | NchFET driver for charge control                                                            |

|                                                       | NchFET driver for discharge control                                                         |

| Power on reset circuit                                | Return from power down mode by detecting voltage and connecting charger                     |

| Series regulator                                      | VREG2 : power supply for MCU (3.3 V or 5.0V)                                                |

| Reset circuit                                         | Series regulator output monitoring (VREG2)                                                  |

| Cell balancing circuit                                | 8 series cells support in RAJ240090                                                         |

|                                                       | 10 series cells support in RAJ240100                                                        |

|                                                       | (On-resistor: 200ohm TYP)                                                                   |

| MCU runaway detection circuit                         | 20 bits×1(2 / 4 / 8 / 16 / 32 / 64 [s] to be selected)                                      |

| AFE On-chip oscillator                                | 4.194 MHz (TYP)                                                                             |

| AFE low speed On-chip oscillator                      | 131.972KHz(TYP)                                                                             |

| AFE timer                                             | 2 channels                                                                                  |

|                                                       | AFE timer A (setting range : 125 ms to 64 s)                                                |

|                                                       | AFE timer B (setting range : 30.52 us to 125 ms)                                            |

| MCU-AFE communication interface(C2C)                  | AFE ~ MCU communication (Chip to Chip Interface)                                            |

| Power supply voltage                                  | VCC = 4.0 to 50 V                                                                           |

| Operation ambient temperature Note2                   | -20 to 85C (REG2T6 bit (bit6 of REG2T)= 0)                                                  |

|                                                       | -40 to 85C (REG2T6 bit (bit6 of REG2T)= 1)                                                  |

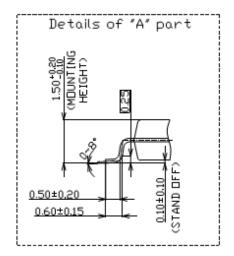

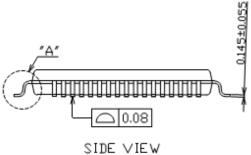

| Package                                               | 64 pin plastic mold LQFP([Body] 10.0mm x 10.0mm , 0.5 mm pitch, 1.4 mm thickness)           |

<R>

<R>

<R>

<R> Note 1. Battery cell voltage and temperature (AN port voltage) detection circuit is only available in RAJ240100.

Note 2. Operation ambient temperature  $T_A = -40$  to 85C is only applicable to RAJ240100.

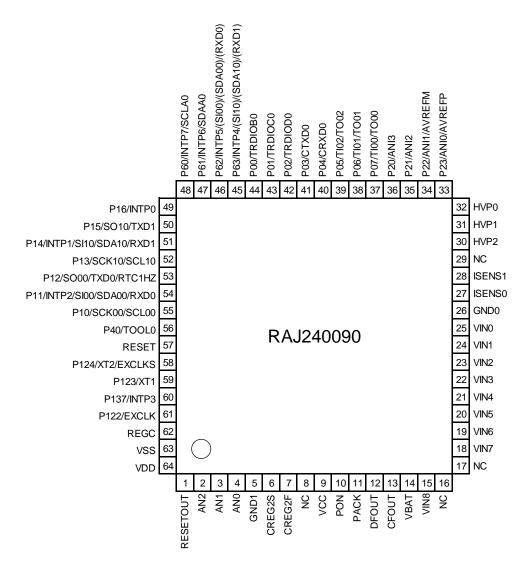

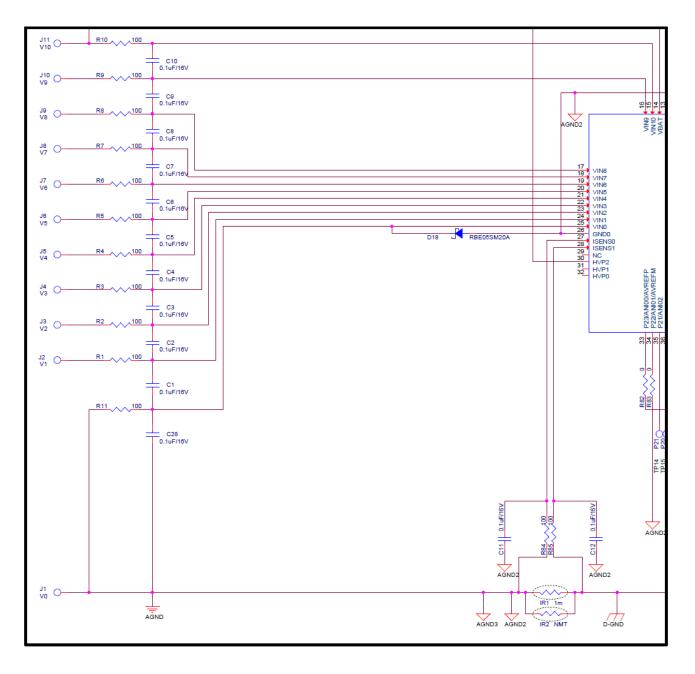

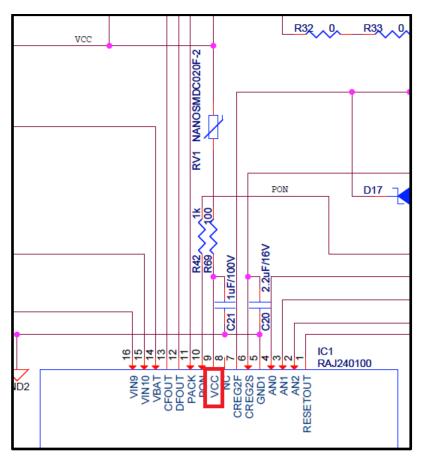

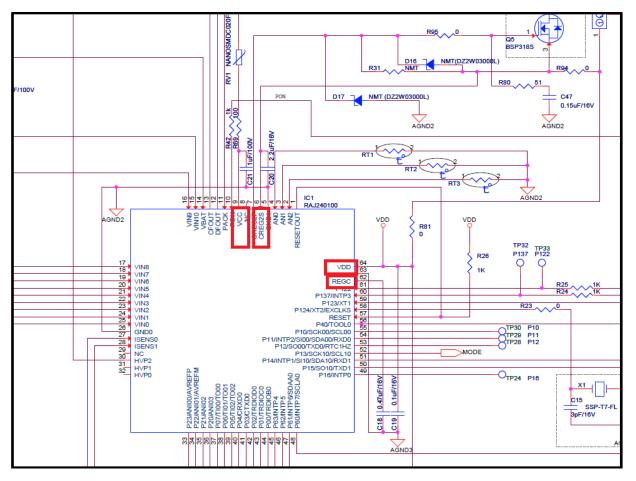

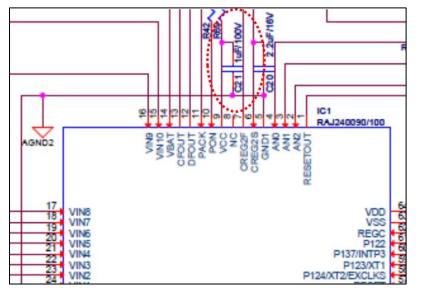

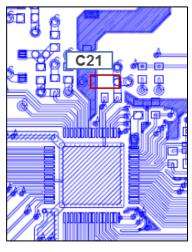

# 2.2 RAJ240090 Pin Configuration

· 64 pin plastic mold LQFP ([Body] 10.0mm x 10.0mm , 0.5 mm pitch)

- Caution 1. REGC pin connects to VSS pin through a capacitor (0.47 to 1µ F)

- Caution 2. CREG2 pin connects to GND0/GND1 pin through a capacitor (1 to 4.7uF).

- Remark 1. Pin name refer to [Section 3.1 pin identification].

- **Remark 2.** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register 0 (PIOR0).

RAJ240090 / RAJ240100

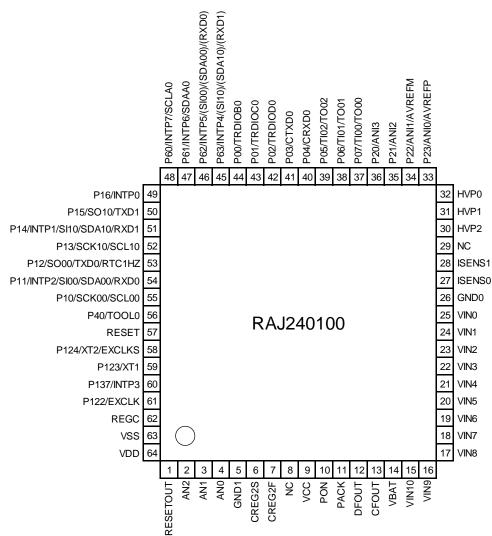

• 64 pin plastic mold LQFP([Body] 10.0mm x 10.0mm , 0.5 mm pitch)

Caution 1. REGC pin connects to VSS pin through a capacitor (0.47 to  $1\mu$  F)

# Caution 2. CREG2 pin connects to GND0/GND1 pin through a capacitor (1 to 4.7uF).

- **Remark 1.** Pin name refer to [Section 3.1 pin identification].

- **Remark 2.** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register 0 (PIOR0).

# 3. PIN FUNCTIONS

# 3.1 Pin identification

| No. | Name                                    | Туре     | Description                                           |

|-----|-----------------------------------------|----------|-------------------------------------------------------|

| 1   | RESETOUT                                | AO       | Reset Output                                          |

| 2   | AN2                                     | AIN      | Analog Input                                          |

| 3   | AN1                                     | AIN      | Analog Input                                          |

| 4   | ANO                                     | AIN      | Analog Input                                          |

| 5   | GND1                                    | Р        | Ground                                                |

| 6   | CREG2S                                  | Р        | Regulator Sense                                       |

| 7   | CREG2F                                  | Р        | Regulator Force                                       |

| 8   | NC                                      | NC       | No connect                                            |

| 9   | VCC                                     | Р        | Power supply                                          |

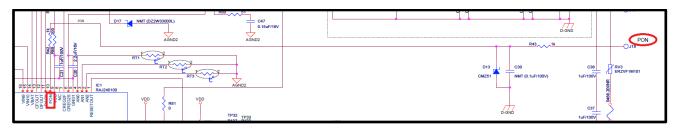

| 10  | PON                                     | HVIN     | High voltage Port for power on                        |

| 11  | РАСК                                    | HVIN     | Charger voltage input                                 |

| 12  | DFOUT                                   | HVO      | Discharge MOSFET control                              |

| 13  | CFOUT                                   | HVO      | Charge MOSFET control                                 |

| 14  | VBAT                                    | AIN      | Battery voltage input                                 |

| 15  | VIN10 for RAJ240100, VIN8 for RAJ240090 | AIN      | Battery voltage input                                 |

| 16  | VIN9 for RAJ240100, NC for RAJ240090    | AIN / NC | Battery voltage input (NC for RAJ240090)              |

| 17  | VIN8 for RAJ240100, NC for RAJ240090    | AIN / NC | Battery voltage input (NC for RAJ240090)              |

| 18  | VIN7                                    | AIN      | Battery voltage input                                 |

| 19  | VIN6                                    | AIN      | Battery voltage input                                 |

| 20  | VIN5                                    | AIN      | Battery voltage input                                 |

| 21  | VIN4                                    | AIN      | Battery voltage input                                 |

| 22  | VIN3                                    | AIN      | Battery voltage input                                 |

| 23  | VIN2                                    | AIN      | Battery voltage input                                 |

| 24  | VIN1                                    | AIN      | Battery voltage input                                 |

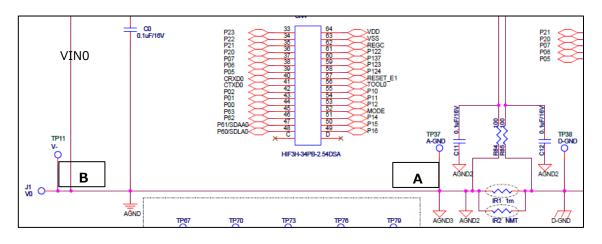

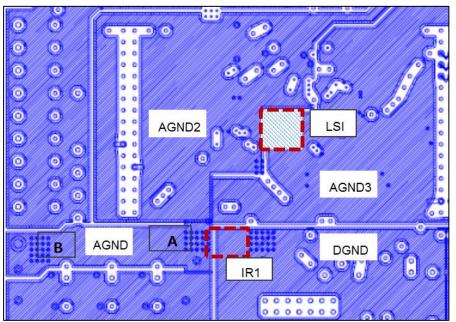

| 25  | VINO                                    | AIN      | Battery voltage input                                 |

| 26  | GND0                                    | Р        | Ground                                                |

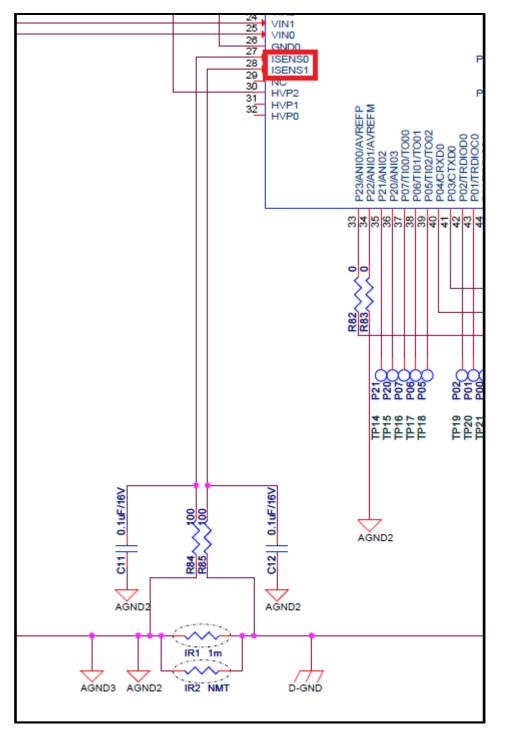

| 27  | ISENS0                                  | AIN      | Analog input for current integration circuit          |

| 28  | ISENS1                                  | AIN      | Analog input for current integration circuit          |

| 29  | NC                                      | NC       | No connect                                            |

| 30  | HVP2                                    | HVIO     | High Voltage Port                                     |

| 31  | HVP1                                    | HVIO     | High Voltage Port                                     |

| 32  | HVP0                                    | HVIO     | High Voltage Port                                     |

| 33  | P23 / ANI0 / AVREFP                     | DIO/AIN  | Port2 / Analog Input / Analog Reference Voltage Plus  |

| 34  | P22 / ANI1 / AVREFM                     | DIO/AIN  | Port2 / Analog Input / Analog Reference Voltage Minus |

| 35  | P21 / ANI2                              | DIO/AIN  | Port2 / Analog Input                                  |

| 36  | P20 / ANI3                              | DIO/AIN  | Port2 / Analog Input                                  |

| 37  | P07 / TI00 / TO00                       | DIO      | Port0 / Timer Input / Timer Output                    |

| 38  | P06 / TI01 / TO01                       | DIO      | Port0 / Timer Input / Timer Output                    |

|     | T                                          |      | (2                                                                                                |

|-----|--------------------------------------------|------|---------------------------------------------------------------------------------------------------|

| No. | Name                                       | Туре | Description                                                                                       |

| 39  | P05 / TI02 / TO02                          | DIO  | Port0 / Timer Input / Timer Output                                                                |

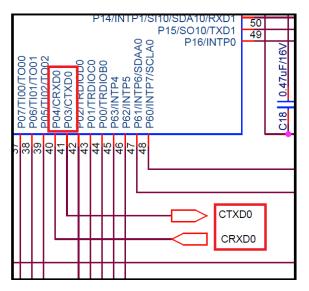

| 40  | P04 / CRXD0                                | DIO  | Port0 / CAN Receive Data                                                                          |

| 41  | P03 / CTXD0                                | DIO  | Port0 / CAN Transmit Data                                                                         |

| 42  | P02 / TRDIOD0                              | DIO  | Port0 / Timer Output                                                                              |

| 43  | P01 / TRDIOC0                              | DIO  | Port0 / Timer Output                                                                              |

| 44  | P00 / TRDIOB0                              | DIO  | Port0 / Timer Output                                                                              |

| 45  | P63 / INTP4 / (SI10) /<br>(SDA10) / (RXD1) | DIO  | Port6 / External Interrupt Input / Serial Data Input /<br>Serial Data Input/Output / Receive Data |

| 46  | P62 / INTP5 / (SI00) /<br>(SDA00) / (RXD0) | DIO  | Port6 / External Interrupt Input / Serial Data Input /<br>Serial Data Input/Output / Receive Data |

| 47  | P61 / INTP6 / SDAA0                        | DIO  | Port6 / External Interrupt Input / I2C Bus data I/O                                               |

| 48  | P60 / INTP7 / SCLA0                        | DIO  | Port6 / External Interrupt Input / I2C Bus clock I/O                                              |

| 49  | P16 / INTP0                                | DIO  | Port1 / External Interrupt Input                                                                  |

| 50  | P15 / SO10 / TXD1                          | DIO  | Port1 / Serial Data Output / Transmit Data                                                        |

| 51  | P14 / INTP1 / SI10 / SDA10 / RXD1          | DIO  | Port1 / External Interrupt Input / Serial Data Input /<br>Serial Data Input/Output / Receive Data |

| 52  | P13 / SCK10 / SCL10                        | DIO  | Port1 / Serial Clock Input/Output                                                                 |

| 53  | P12 / SO00 / TXD0 / RTC1HZ                 | DIO  | Port1 / Serial Data Output / Transmit Data /<br>Real-time Clock Correction Clock (1 Hz) Output    |

| 54  | P11 / INTP2 / SI00 / SDA00 / RXD0          | DIO  | Port1 / External Interrupt Input / Serial Data Input /<br>Serial Data Input/Output / Receive Data |

| 55  | P10 / SCK00 / SCL00                        | DIO  | Port1 / Serial Clock Input/Output                                                                 |

| 56  | P40 / TOOL0                                | DIO  | Port4 / Data Input/Output for Tool                                                                |

| 57  | RESET                                      | DIN  | Reset Input for MCU                                                                               |

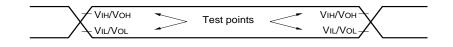

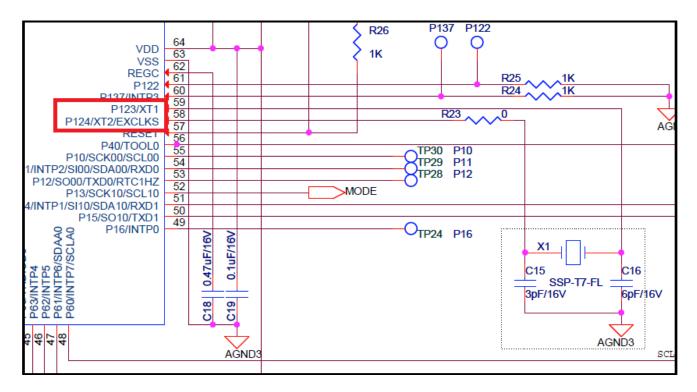

| 58  | P124 / XT2 / EXCLKS                        | DI   | Port12 / Crystal Oscillator Input / External Clock Input                                          |

| 59  | P123 / XT1                                 | DI   | Port12 / Crystal Oscillator Input                                                                 |

| 60  | P137 / INTP3                               | DI   | Port13 / External Interrupt Input                                                                 |

| 61  | P122/EXCLK                                 | DI   | Port12 / External Clock Input                                                                     |

| 62  | REGC                                       | Р    | Regulator Capacitance                                                                             |

| 63  | VSS                                        | Р    | Ground                                                                                            |

| 64  | VDD                                        | Р    | Power Supply                                                                                      |

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register 0 (PIOR0).

| HVO: high voltage output        | DIO: | digital I/O   |

|---------------------------------|------|---------------|

| HVIN: high voltage input        | DIN: | digital input |

| HVIO: high voltage input/output | AIN: | analog input  |

| P: power                        | AO:  | analog output |

### 3.2 Pin Functions

3.2.1 Pin type and alternate functions

| Function<br>name | Pin Type | I/O   | After Reset<br>Release | Alternate Function          | Function                                                                                                                                                                  |

|------------------|----------|-------|------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00              | 7-1-7    | I/O   | Input port             | TRDIOB0                     | Port 0.                                                                                                                                                                   |

| P01              | 7-1-7    |       |                        | TRDIOC0                     | 8-bit I/O port.                                                                                                                                                           |

| P02              | 7-1-7    |       |                        | TRDIOD0                     | Input/output can be specified in 1-bit unit.                                                                                                                              |

| P03              | 8-1-4    |       |                        | CTXD0                       | Use of an on-chip pull-up resistor can be specified by a software setting at input port.                                                                                  |

| P04              | 8-1-4    |       |                        | CRXD0                       | Input of P03 and P04 can be set to TTL input                                                                                                                              |

| P05              | 7-1-3    |       |                        | TI02/TO02                   | buffer.                                                                                                                                                                   |

| P06              | 7-1-3    |       |                        | TI01/TO01                   | Output of P03 and P04 can be set to N-ch open                                                                                                                             |

| P07              | 7-1-3    |       |                        | TI00/TO00                   | drain output (VDD tolerance).                                                                                                                                             |

| P10              | 8-1-4    | I/O   | Input port             | SCK00/SCL00                 | Port 1.                                                                                                                                                                   |

| P11              | 8-1-4    |       |                        | INTP2/SI00/SDA00/RXD0       | 7-bit I/O port.                                                                                                                                                           |

| P12              | 7-1-4    |       |                        | SO00/TXD0/RTC1HZ            | Input/output can be specified in 1-bit unit.                                                                                                                              |

| P13              | 8-1-4    |       |                        | SCK10/SCL10                 | Use of an on-chip pull-up resistor can be<br>specified by a software setting at input port.                                                                               |

| P14              | 8-1-4    |       |                        | INTP1/SI10/SDA10/RXD1       | Input of P10 to P14 can be set to TTL input                                                                                                                               |

| P15              | 7-1-4    |       |                        | SO10/TXD10                  | buffer.                                                                                                                                                                   |

| P16              | 7-1-4    |       |                        | INTP0                       | Output of P10 to P16 can be set to N-ch open<br>drain output (VDD tolerance).                                                                                             |

| P20              | 4-3-3    | I/O   | Analog                 | ANI3                        | Port 2.                                                                                                                                                                   |

| P21              | 4-3-3    |       | function               | ANI2                        | 4-bit I/O port.                                                                                                                                                           |

| P22              | 4-3-3    |       |                        | ANI1/AVREFM                 | Input/output can be specified in 1-bit unit.                                                                                                                              |

| P23              | 4-3-3    |       |                        | ANI0/AVREFP                 | Can be set to analog input <sup>Note 1.</sup>                                                                                                                             |

| P30              | 7-1-3    | I/O   | Input port             | INTP13                      | Port 3. Note 2.                                                                                                                                                           |

| P31              | 7-1-3    |       |                        | INTP12                      | 4-bit I/O port.                                                                                                                                                           |

| P32              | 7-1-3    |       |                        | INTP11                      | Input/output can be specified in 1-bit unit.                                                                                                                              |

| P33              | 7-1-3    |       |                        | INTP10                      | Use of an on-chip pull-up resistor can be specified by a software setting at input port.                                                                                  |

| P40              | 7-1-3    | I/O   | Input port             | TOOLO                       | Port 4.<br>1-bit I/O port.<br>Input/output can be specified in 1-bit unit.<br>Use of an on-chip pull-up resistor can be<br>specified by a software setting at input port. |

| P60              | 12-1-2   | I/O   | Input port             | INTP7/SCLA0                 | Port 6.                                                                                                                                                                   |

| P61              | 12-1-2   |       |                        | INTP6/SDAA0                 | 4-bit I/O port.                                                                                                                                                           |

| P62              | 12-1-2   |       |                        | INTP5/(SI00)/(SDA00)/(RXD0) | Input/output can be specified in 1-bit unit.                                                                                                                              |

| P63              | 12-1-2   |       |                        | INTP4/(SI10)/(SDA10)/(RXD1) | Output of P60 to P63 can be set to N-ch open drain output (6.0V tolerance).                                                                                               |

| P70              | 7-1-3    | I/O   | Input port             | INTP9                       | Port 7. Note 2.                                                                                                                                                           |

| P71              | 7-1-3    |       |                        | INTP8                       | 8-bit I/O port.                                                                                                                                                           |

| P72              | 7-1-3    |       |                        | EXBSEL                      | Input/output can be specified in 1-bit unit.<br>Use of an on-chip pull-up resistor can be                                                                                 |

| P73              | 7-1-3    |       |                        | EXBCK                       | specified by a software setting at input port.                                                                                                                            |

| P74              | 7-1-3    |       |                        | EXBO0/EXBI0                 |                                                                                                                                                                           |

| P75              | 7-1-3    |       |                        | EXBO1/EXBI1                 |                                                                                                                                                                           |

| P76              | 7-1-3    |       |                        | EXBO2/EXBI2                 |                                                                                                                                                                           |

| P77              | 7-1-3    |       |                        | EXBO3/EXBI3                 |                                                                                                                                                                           |

| P122             | 2-2-2    | input | Input port             | EXCLK                       | Port 12.                                                                                                                                                                  |

| P123             | 2-2-1    |       |                        | XT1                         | 3-bit input-only port.                                                                                                                                                    |

| P124             | 2-2-1    |       |                        | XT2/EXCLKS                  |                                                                                                                                                                           |

| P137             | 2-1-2    | input | Input port             | INTP3                       | Port 13.<br>1-bit input-only port.                                                                                                                                        |

| RESET            | 2-1-1    | input | -                      | -                           | Input-only pin for external reset.<br>Connect to VDD directly or via a resistor wher<br>external reset is not used.                                                       |

**Note 1.** Each pin can be configured as digital or analog pin by setting the port mode in the control register x (PMCx) (Can be specified in 1-bit units).

**Note 2.** Connected to internal AFE circuit.

### 3.2.2 External Pin Functions

| Category                                                      | Pin name                      | I/O    | Function                                                                                                                                      |  |

|---------------------------------------------------------------|-------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power supply                                                  | VCC                           | _      | Power supply input<br>Apply power supply voltage to VCC pin from a charger or battery.                                                        |  |

|                                                               | GND0、GND1                     | -      | Device ground input. Connect the negative input terminal of lithium-ion ba<br>1 to the GND0 and GND1 pins                                     |  |

|                                                               | CREG2F                        | —      | Series regulator force port                                                                                                                   |  |

|                                                               | CREG2S                        | -      | Series regulator sense port<br>Connect to GND0 and GND1 via a capacitor (1uF to 4.7uF)                                                        |  |

|                                                               | VDD                           | -      | Positive power supply for MCU<br>Connect to CREG2                                                                                             |  |

|                                                               | VSS                           | -      | Ground input for MCU                                                                                                                          |  |

|                                                               |                               |        | Connect the negative input terminal of lithium-ion battery 1 to the GND0 and GND1 pins                                                        |  |

|                                                               | REGC Note 1.                  | -      | Pin for connecting regulator output stabilization capacitance for internal operation. Connect this pin to VSS via a capacitor (0.47 to 1 uF). |  |

|                                                               |                               |        | Also, use a capacitor with good characteristics, since it is used to stabilize internal voltage.                                              |  |

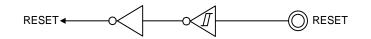

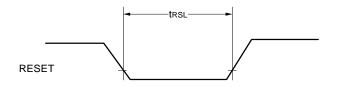

| RESET                                                         | RESET                         | Input  | This is the active-low system reset input pin for MCU.                                                                                        |  |

|                                                               | RESETOUT                      | output | This is the active-low system reset output pin for AFE.                                                                                       |  |

| TOOL0                                                         | TOOL0 Note 2                  | input  | Data I/O for flash memory programmer/debugger.<br>Connect to the VDD via an external pull-up resistor in the on chip debug mode               |  |

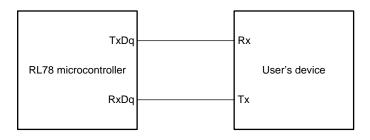

| Serial interface                                              | RxD0, RxD1                    | input  | Serial data input pins of serial interface UART0 to UART1                                                                                     |  |

| (UART0, UART1)                                                | TxD0, TxD1                    | output | Serial data output pins of serial interface UART0 to UART1                                                                                    |  |

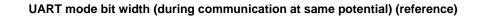

| Serial interface                                              | SCK00,SCK10                   | I/O    | Serial clock I/O pins of serial interface CSI00 and CSI10                                                                                     |  |

| (CSI00, CSI10)                                                | SI00, SI10                    | input  | Serial data input pins of serial interface CSI00 and CSI10                                                                                    |  |

|                                                               | SO00, SO10                    | output | Serial data output pins of serial interface CSI00 and CSI10                                                                                   |  |

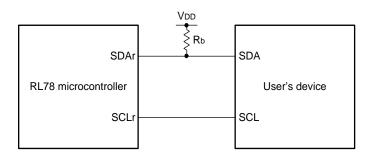

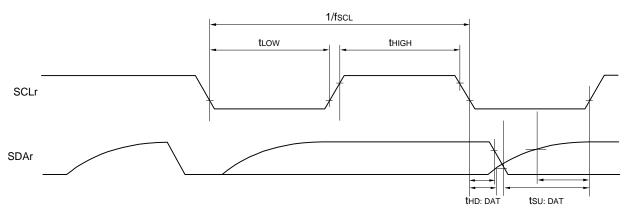

| Serial interface                                              | SCL00, SCL10                  | output | Serial clock output pins of serial interface IIC00 and IIC10                                                                                  |  |

| (IIC00, IIC10)                                                | SDA00, SDA10                  | I/O    | Serial data I/O pins of serial interface IIC00 and IIC10                                                                                      |  |

| Serial interface                                              | SCLA0                         | I/O    | Serial clock I/O pins of serial interface IICA0                                                                                               |  |

| (IICA0)                                                       | SDAA0                         | I/O    | Serial data I/O pins of serial interface IICA0,                                                                                               |  |

| CAN-BUS interface                                             | CRXD0                         | input  | CAN serial data input                                                                                                                         |  |

|                                                               | CTXD0                         | output | CAN serial data output                                                                                                                        |  |

| A/D converter                                                 | AN0, AN1, AN2                 | input  | AFE A/D converter analog input                                                                                                                |  |

|                                                               | ANIO, ANI1,<br>ANI2, ANI3     | input  | MCU A/D converter analog input                                                                                                                |  |

|                                                               | AVREFP                        | input  | A/D converter reference voltage (+ side).                                                                                                     |  |

|                                                               | AVREFM                        | input  | A/D converter reference voltage (- side).                                                                                                     |  |

| Current integration circuit and overcurrent detection circuit | ISENS0, ISENS1                | input  | Analog input for current integration circuit and over current detection circuit                                                               |  |

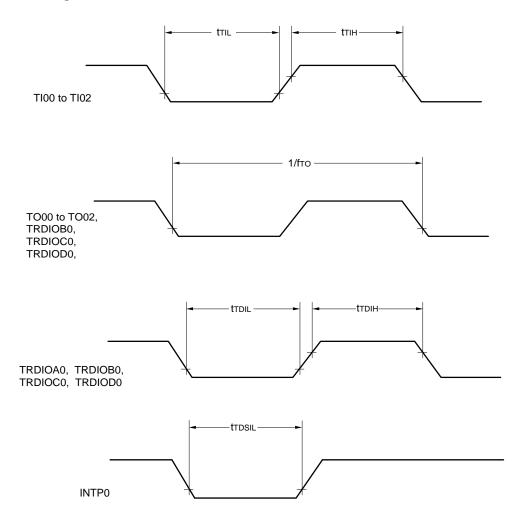

| Timer                                                         | TI00-TI02                     | input  | The pins for inputting an external count clock/capture trigger to 16-bit timers 00 to 02                                                      |  |

|                                                               | TO00-TO02                     | output | Timer output pins of 16-bit timers 00 to 02                                                                                                   |  |

|                                                               | TRDIOB0<br>TRDIOC0<br>TRDIOD0 | I/O    | Timer RD input/output                                                                                                                         |  |

|                                                               | RTC1HZ                        | output | Real-time clock supports clock (1 Hz) output                                                                                                  |  |

|                                   |                                                                                 |        | (2                                                                                                                                          |  |  |

|-----------------------------------|---------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Category                          | Pin name                                                                        | I/O    | Function                                                                                                                                    |  |  |

| High voltage I/O port             | HVP0, HVP1,<br>HVP2                                                             | I/O    | High voltage I/O in correspondence with VCC tolerance                                                                                       |  |  |

| Subsystem clock                   | tem clock XT1, XT2 <sup>Note 3</sup> – Resonator connection for subsystem clock |        | Resonator connection for subsystem clock                                                                                                    |  |  |

| External clock                    | EXCLK                                                                           | Input  | External clock input for main system clock                                                                                                  |  |  |

|                                   | EXCLKS                                                                          | input  | External clock input for subsystem clock                                                                                                    |  |  |

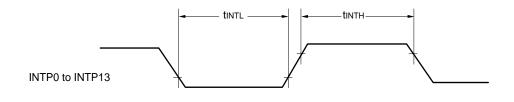

| External interrupt input          | INTP0 to INTP13                                                                 | input  | nterrupt request input pin. INTP8 to INTP13 connects interrupt request signal<br>of AFE in the package and do not connect to any pin        |  |  |

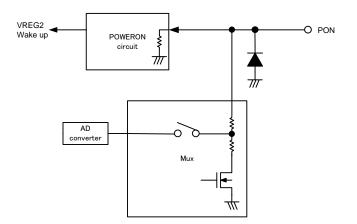

| Power on circuit                  | PON                                                                             | input  | Power on input for release from power down state                                                                                            |  |  |

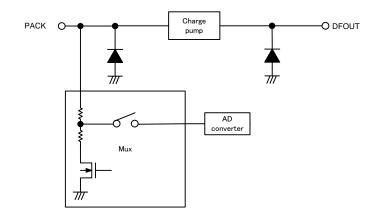

| Charger connection detect         | PACK                                                                            | Input  | Charger voltage input and source voltage of discharge FET drive port (DFOUT)                                                                |  |  |

| Battery connection detect         | VBAT                                                                            | input  | Sense voltage input pin for most positive cell and source voltage for charge FET drive port (CFOUT)                                         |  |  |

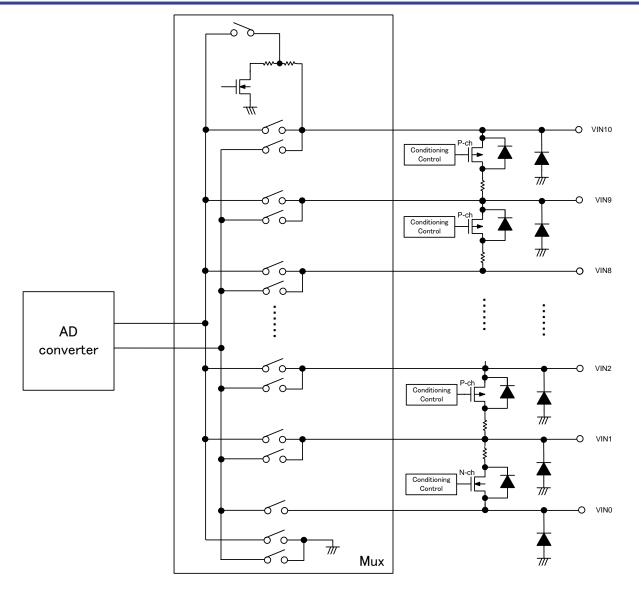

| Battery voltage detection circuit | VIN10 Note 4                                                                    | input  | The positive input terminal of lithium-ion battery 10.                                                                                      |  |  |

|                                   | VIN9 Note 4                                                                     | Input  | The negative input terminal of lithium-ion battery 10 and the positive input terminal of lithium-ion battery 9                              |  |  |

|                                   | VIN8                                                                            | Input  | The negative input terminal of lithium-ion battery 9 and the positive input terminal of lithium-ion battery 8                               |  |  |

|                                   | VIN7                                                                            | Input  | The negative input terminal of lithium-ion battery 8 and the positive input terminal of lithium-ion battery 7                               |  |  |

|                                   | VIN6                                                                            | Input  | The negative input terminal of lithium-ion battery 7 and the positive input terminal of lithium-ion battery 6                               |  |  |

|                                   | VIN5                                                                            | Input  | The negative input terminal of lithium-ion battery 6 and the positive input terminal of lithium-ion battery 5                               |  |  |

|                                   | VIN4                                                                            | Input  | The negative input terminal of lithium-ion battery 5 and the positive input terminal of lithium-ion battery 4                               |  |  |

|                                   | VIN3                                                                            | Input  | The negative input terminal of lithium-ion battery 4 and the positive input terminal of lithium-ion battery 3                               |  |  |

|                                   | VIN2                                                                            | Input  | The negative input terminal of lithium-ion battery 3 and the positive input terminal of lithium-ion battery 2                               |  |  |

|                                   | VIN1                                                                            | Input  | The negative input terminal of lithium-ion battery 2 and the positive input terminal of lithium-ion battery 1                               |  |  |

|                                   | VIN0                                                                            | Input  | The negative input terminal of lithium-ion battery 1                                                                                        |  |  |

| FET control output                | DFOUT                                                                           | Output | ON/OFF signal output pin for discharge FET.                                                                                                 |  |  |

|                                   | CFOUT                                                                           | Output | ON/OFF signal output pin for charge FET.                                                                                                    |  |  |

| Communication between AFE and MCU | P72                                                                             | input  | Control signal of communication between AFE and MCU with setting to output port. P72 is connected to AFE in a package and not external pin. |  |  |

|                                   | EXBCK                                                                           | Output | Clock signal of communication between AFE and MCU                                                                                           |  |  |

|                                   | EXBD0-3                                                                         | I/O    | Data signal of communication between AFE and MCU                                                                                            |  |  |

**Note 1.** REGC is not external power supply pin. (Do not draw current from REGC.)

**Note 2.** After reset release, the connection between P40/TOOL0 and the operating mode are as follows.

| P40/TOOL0 | Operation Mode                |

|-----------|-------------------------------|

| VDD       | Normal operation mode         |

| 0V        | Flash memory programming mode |

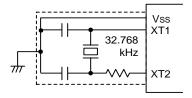

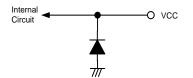

Note 3. Figure 3-1 shows an example of the external circuit for the XT1 oscillator

Figure 3-1 Example of External Circuit for XT1 Oscillator

**Note 4.** VIN10 pin and VIN9 pin are only applicable to RAJ240100.

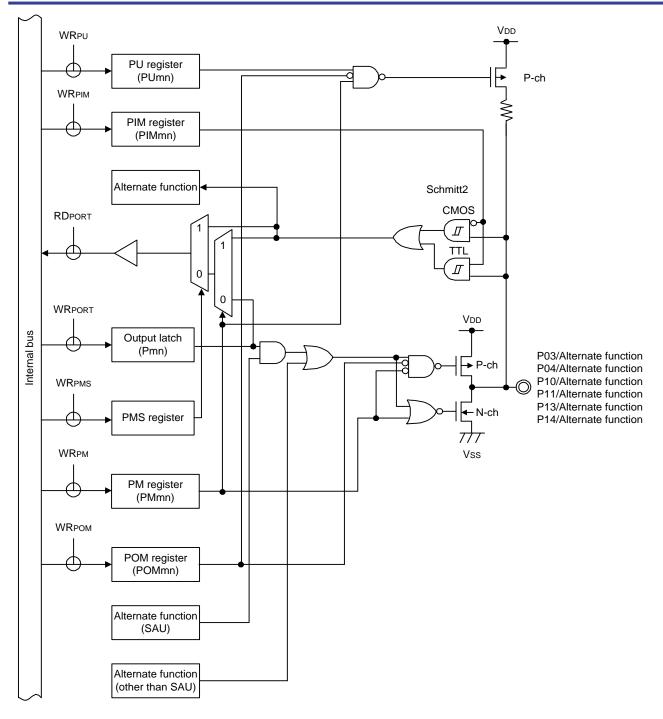

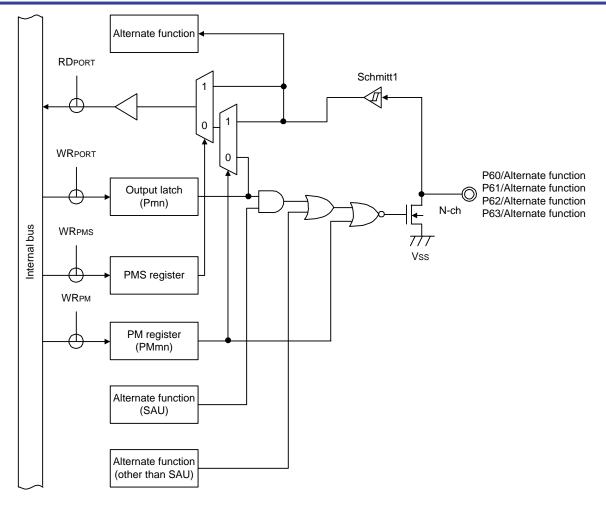

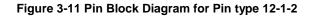

# 3.3 Pin Block Diagram

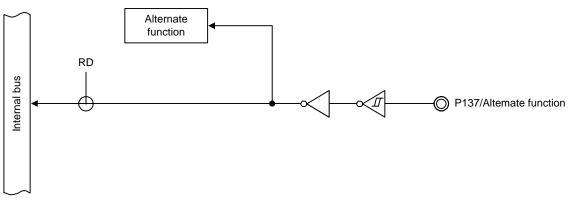

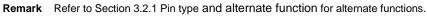

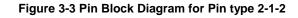

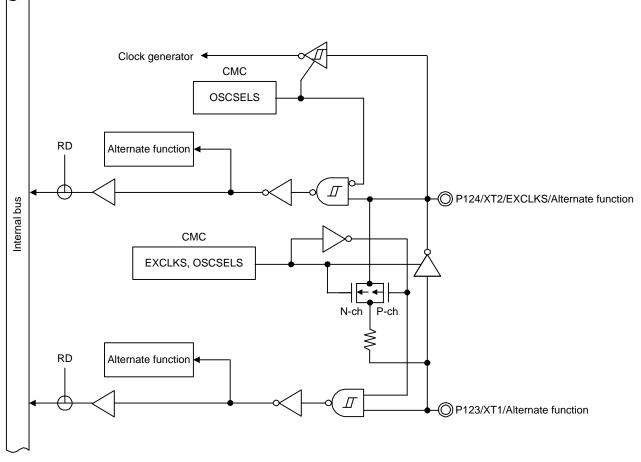

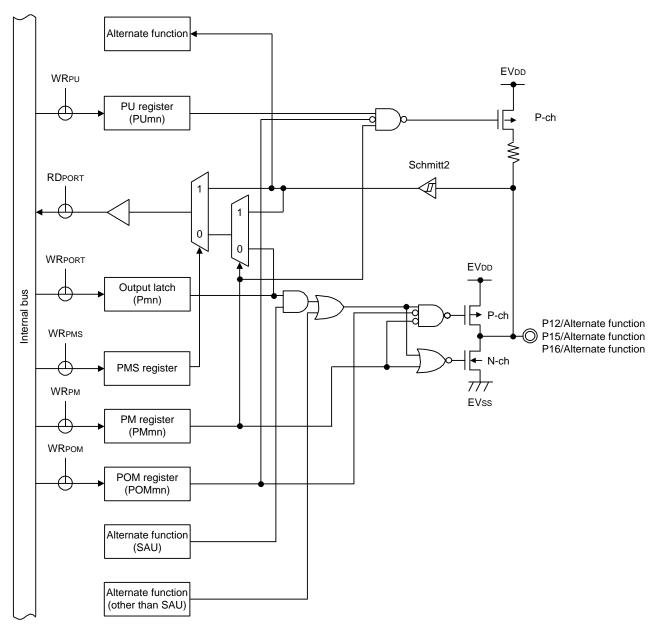

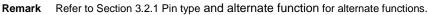

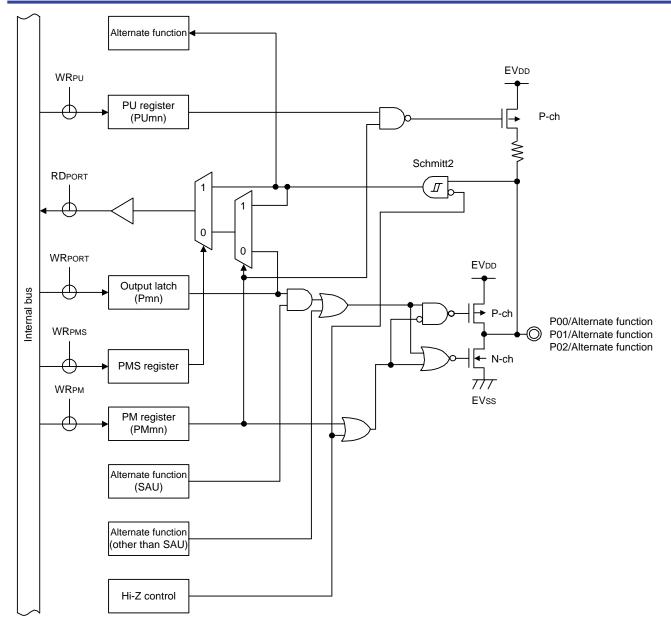

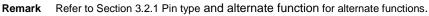

**Remark** Refer to Section 3.2.1 Pin type and alternate function for alternate functions.

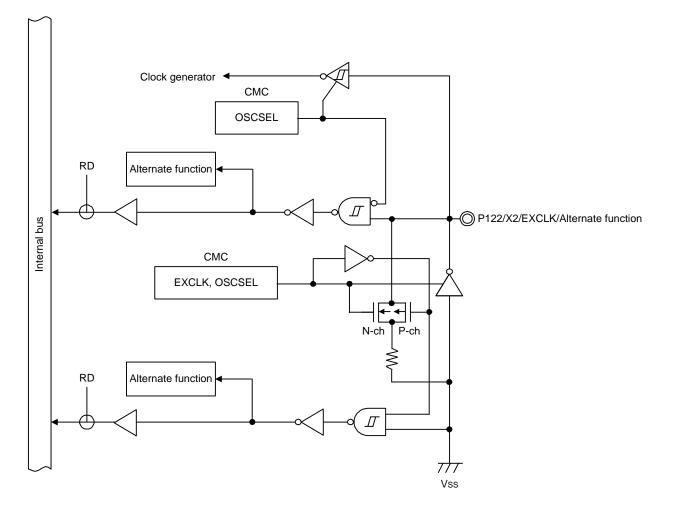

#### Figure 3-4 Pin Block Diagram for Pin type 2-2-1

Figure 3-5 Pin Block Diagram for Pin type 2-2-2

Remark Refer to Section 3.2.1 Pin type and alternate function for alternate functions.

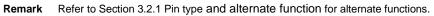

Figure 3-6 Pin Block Diagram for Pin type 4-3-3

Remark Refer to Section 3.2.1 Pin type and alternate function for alternate functions.

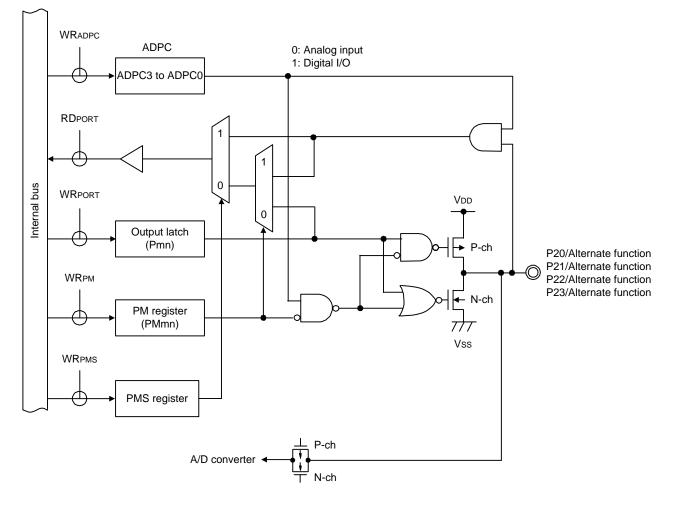

Figure 3-7 Pin Block Diagram for Pin type 7-1-3

#### Figure 3-8 Pin Block Diagram for Pin type 7-1-4

#### Figure 3-9 Pin Block Diagram for Pin type 7-1-7

**Remark** Refer to Section 3.2.1 Pin type and alternate function for alternate functions.

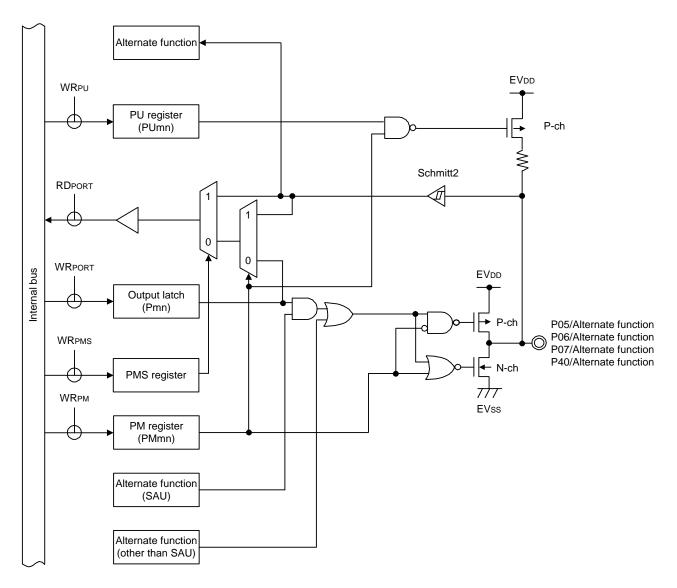

Figure 3-10 Pin Block Diagram for Pin type 8-1-4

**Remark** Refer to Section 3.2.1 Pin type and alternate function for alternate functions.

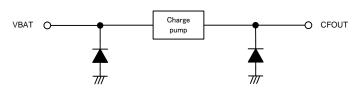

Figure 3-12 Pin Block Diagram for VCC Pin

Figure 3-13 Pin Block Diagram for VBAT and CFOUT Pin

Figure 3-14 Pin Block Diagram for VPACK and DFOUT Pin

Figure 3-15 Pin Block Diagram for PON Pin

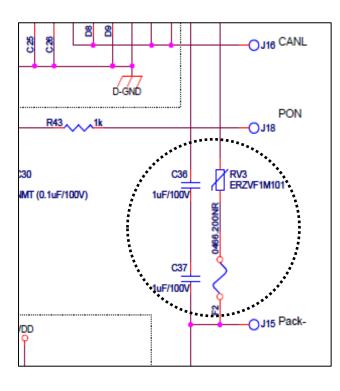

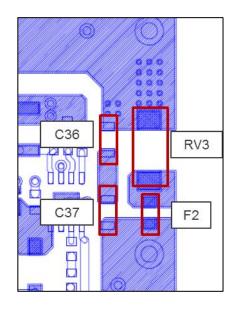

- Caution 1. VIN10 pin and VIN9 pin are only applicable to RAJ240100.

- Caution 2. For RAJ240090, VIN8 pin is connected to ladder resistors.

Figure 3-16 Pin Block Diagram for VIN10 to VIN0 Pin

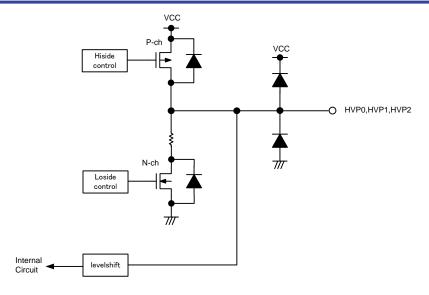

Figure 3-17 Pin Block Diagram for HVP0, HVP1 and HVP2 Pin

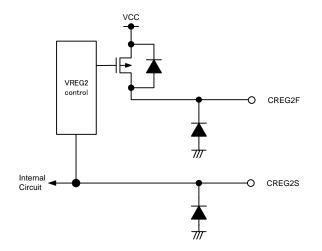

Figure 3-18 Pin Block Diagram for CREG2F and CREG2S Pin

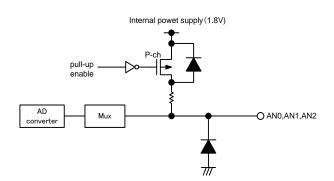

Figure 3-19 Pin Block Diagram for AN0, AN1 and AN2 Pin

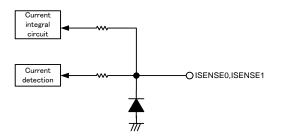

Figure 3-20 Pin Block Diagram for ISENS0 and ISENS1 Pin

### <R> 4. ELECTRICAL SPECIFICATIONS

Caution This product has an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

**Remark 1.** Specifications for VIN10 pin and VIN9 pin are only applicable to RAJ240100. **Remark 2.** Operation ambient temperature  $T_A = -40$  to 85C is only applicable to RAJ240100.

### 4.1 Absolute Maximum Ratings

Absolute Maximum Ratings

| Parameter                 | Symbols         |                                                                         | Conditions                                                                                                    | Ratings                                                     | Unit |

|---------------------------|-----------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|

| Supply voltage            | Vcc             | VCC                                                                     | Contailone                                                                                                    | -0.5 to +60.0                                               | V    |

| Cuppiy Vollage            | VDD             | VDD                                                                     |                                                                                                               | -0.5 to +6.5                                                | v    |

|                           | GND             | GND0, GN                                                                | ID1. VSS                                                                                                      | -0.5 to 0.3                                                 | v    |

| CREG2 pin input voltage   | VCREG2          |                                                                         |                                                                                                               | -0.5 to +60.0                                               | V    |

| on 202 phillipat ronago   | 1011202         | CREG2S                                                                  |                                                                                                               | -0.3 to 6.5 Note 2                                          | V    |

| REGC pin input voltage    | Viregc          | REGC                                                                    |                                                                                                               | -0.3 to 2.8 and                                             | V    |

|                           |                 |                                                                         |                                                                                                               | -0.3 to (VDD+0.3) Note 1                                    | -    |

| Input voltage             | VI1             |                                                                         | 7, P10 to P16, P20 to 23,<br>L0), P122 to P124, P137, RESET                                                   | -0.3 to (VDD+0.3) Note 3                                    | V    |

|                           | VI2             | P60 to P63                                                              | B(N-ch open-drain)                                                                                            | -0.3 to +6.5                                                | V    |

|                           | VIN-H1          |                                                                         | 19, VIN8, VIN7, VIN6, VIN5, VIN4,<br>2, VIN1, VBAT, PACK, PON,                                                | -0.5 to +60.0                                               | V    |

|                           | VIN-H2          | HVP0, HV                                                                | P1, HVP2                                                                                                      | -0.5 to (VDD+0.3) Note 5                                    | V    |

|                           | VIN-B           | VIN7 to VI                                                              | /IN9, VIN9 to VIN8, VIN8 to VIN7,<br>N6, VIN6 to VIN5, VIN5 to VIN4,<br>N3, VIN3 to VIN2, VIN2 to VIN1,<br>N0 | -0.5 to +6.5                                                | V    |

|                           | VIN-M           | VIN0                                                                    |                                                                                                               | -0.5 to +5.0                                                | V    |

|                           | VIN-L           | AN0, AN1,                                                               | AN2, ISENS0, ISENS1                                                                                           | -0.5 to +2.0                                                | V    |

|                           | Vai             | ANI00 to A                                                              | NI03                                                                                                          | -0.3 to VDD +0.3<br>and -0.3 to AVREF(+)<br>+0.3 Notes 3, 4 | V    |

| Output voltage            | Vo1             | P00 to P07, P10 to P16, P20 to 23,<br>P40 (TOOL0), P123, P124, RESETOUT |                                                                                                               | -0.3 to (VDD+0.3) Note 3                                    | V    |

|                           | Vo-н            | CFOUT, D                                                                | FOUT, HVP0, HVP1, HVP2                                                                                        | -0.5 to +60.0                                               | V    |

| High-level output current | Іон1            | Per pin                                                                 | P00 to P07, P10 to P16,<br>P40 (TOOL0)                                                                        | -40                                                         | mA   |

|                           |                 | Total of<br>all pins                                                    | P00 to P07, P10 to P16,<br>P40 (TOOL0)                                                                        | -70                                                         | mA   |

|                           | Іон2            | Per pin                                                                 | P20 to P23                                                                                                    | -0.5                                                        | mA   |

|                           |                 | Total of<br>all pins                                                    | P20 to P23                                                                                                    | -2.0                                                        | mA   |

| Low-level output current  | IOL1            | Per pin                                                                 | P00 to P07, P10 to P16,<br>P40 (TOOL0)                                                                        | +40                                                         | mA   |

|                           |                 | Total of<br>all pins                                                    | P00 to P07, P10 to P16,<br>P40 (TOOL0), P60 to P63                                                            | +70                                                         | mA   |

| Power consumption         | Pd              | Topr = 25 C                                                             |                                                                                                               | 300                                                         | mW   |

| Operating ambient         | ТА              | REG2T6 bit = 0                                                          |                                                                                                               | -20 to +85                                                  | С    |

| Temperature               | T <sub>AL</sub> | REG2T6 bit = 1                                                          |                                                                                                               | -40 to +85                                                  | С    |

| Storage temperature       | Tstg            | -                                                                       |                                                                                                               | -65 to +150                                                 | С    |

(Note, Caution and Remark are listed on next page.)

### RAJ240090 / RAJ240100

- Note 1. Connect the REGC pin to VSS via a capacitor (0.47 to 1uF). This value regulates the absolute maximum rating of the REGC pin. Do not use this pin with voltage applied to it.

- Note 2. Connect the CREG2 pin to GND0 or GND1 via a capacitor (2.2uF). This value regulates the absolute maximum rating of the CREG2 pin.

Note 3. Must be 6.5V or lower.

Note 4. Do not exceed AVREF (+) + 0.3V in case of A/D conversion target pin.

Note 5. Must be 60V or lower.

Caution Product quality may degrade if the absolute maximum rating has been exceeded. The absolute maximum ratings are rated values where the product is on the verge of suffering physical damage, therefore the product must be used within conditions that ensure the absolute maximum ratings are not exceeded.

Remark 1. Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

**Remark 2.** AVREF (+): + side reference voltage of the A/D converter.

Remark 3. GND (GND0, GND1 and VSS): Reference voltage.

# 4.2 Power supply voltage condition

| Parameter    | Symbol    | Conditions      | MIN. | TYP. | MAX. | Unit |

|--------------|-----------|-----------------|------|------|------|------|

| Power supply | VCC, VBAT |                 | 4.0  | -    | 50.0 | V    |

|              | VDD       |                 | 2.7  | -    | 5.5  | V    |

|              | GND       | GND0, GND1, VSS | -    | 0.0  | -    | V    |

### 4.3 Supply current characteristics

$(T_A = -40/-20 \text{ to } +85C, 4.0V \le VCC \le 50V, VDD = CREG2, GND0 = GND1 = 0V)$

| Parameter                                     | Symbol | Conditions                                                                                                                                                                                                                                                                                         | MIN. | TYP. | MAX.  | Unit |

|-----------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| Power down mode<br>current 1                  | IPD    | VCC=35V                                                                                                                                                                                                                                                                                            |      |      | 2.0   | uA   |

| Power down mode<br>current 2<br>(Low voltage) | IPDL   | VCC=4.0V                                                                                                                                                                                                                                                                                           |      |      | 1.0   | uA   |

| Sleep mode current 1                          | ISLP1  | $-20C \le T_A \le 85C$ , REG2T6 bit = 0,<br>MCU operation mode: STOP mode<br>ALOCO = ON, AOCO = OFF<br>CD = ALL ON, AFE Timer = ON,<br>AFE WDT = ON, CFOUT = L, DFOUT = L,<br>AD(AFE) = OFF, CC = OFF                                                                                              |      | 25.0 | 50.0  | uA   |

|                                               | ISLP1L | $\label{eq:tau} \begin{array}{l} -40C \leq T_A \leq 85C, \mbox{ REG2T6 bit = 1,} \\ MCU \mbox{ operation mode: STOP mode} \\ ALOCO = ON, \mbox{ AOCO = OFF} \\ CD = ALL \mbox{ ON, AFE Timer = ON,} \\ AFE \mbox{ WDT = ON, CFOUT = L, DFOUT = L,} \\ AD(AFE) = OFF, \mbox{ CC = OFF} \end{array}$ |      | 35   | 70.0  | uA   |

| Sleep mode current 2                          | ISLP2  | -20C $\leq$ T <sub>A</sub> $\leq$ 85C, REG2T6 bit = 0,<br>MCU operation mode: STOP mode<br>ALOCO = ON, AOCO = OFF<br>CD = ALL ON, AFE timer = ON,<br>AFE WDT = ON, CFOUT = H, DFOUT = H,<br>AD(AFE) = OFF, CC = OFF                                                                                |      | 50.0 | 100.0 | uA   |

|                                               | ISLP2L | -40C $\leq$ T <sub>A</sub> $\leq$ 85C, REG2T6 bit = 1,<br>MCU operation mode: STOP mode<br>ALOCO = ON, AOCO = OFF<br>CD = ALL ON, AFE timer = ON,<br>AFE WDT = ON, CFOUT = H, DFOUT = H,<br>AD(AFE) = OFF, CC = OFF                                                                                |      | 60   | 120.0 | uA   |

| Normal mode current                           | Ілом   | MCU operation mode: LS (Low-Speed main)<br>mode, fHOCO=8MHz<br>ALOCO = ON, AOCO = ON<br>CD = ALL ON, AFE Timer = ON,<br>AFE WDT = ON, CFOUT = H, DFOUT = H,<br>AD(AFE) = ON, CC = ON                                                                                                               |      | 2.0  | 3.0   | mA   |

Caution 1. After trimming.

Caution 2. When RAJ240100 is used in T<sub>A</sub> = -40 to 85C, REG2T6 (bit 6 of REG2T register) must be set to "1".

### 4.4 Oscillator Characteristics

### 4.4.1 XT1 Characteristics

$(T_A = -40/-20 \text{ to } +85C, 2.7V \le VDD \le 5.5V, GND0 = GND1 = VSS = 0V)$

| Parameter                                  | Resonator         | Conditions | MIN. | TYP.   | MAX. | Unit |

|--------------------------------------------|-------------------|------------|------|--------|------|------|

| XT1 clock oscillation frequency (fxT) Note | Crystal resonator |            | 32   | 32.768 | 35   | kHz  |

**Note** Indicates only permissible oscillator frequency ranges. Refer to AC Characteristics for instruction execution time. Request evaluation by the manufacturer of the oscillator circuit mounted on a board to check the oscillator characteristics.

Caution When RAJ240100 is used in T<sub>A</sub> = -40 to 85C, REG2T6 (bit 6 of REG2T register) must be set to "1".

### 4.4.2 MCU On-chip oscillator characteristics

$(T_A = -40/-20 \text{ to } +85C, 2.7V \le VDD \le 5.5V, GND0 = GND1 = VSS = 0V)$

| Parameter                                               | Symbol | Conditions             | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------|--------|------------------------|------|------|------|------|

| High-speed on-chip oscillator clock frequency Note 1, 2 | fін    |                        | 1    |      | 32   | MHz  |

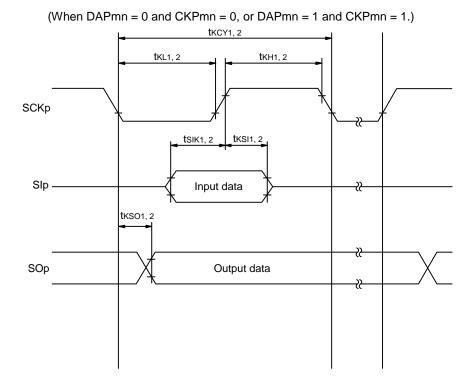

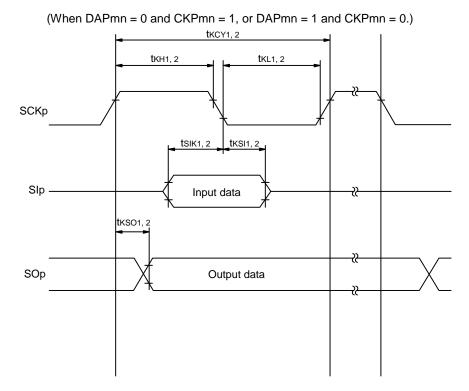

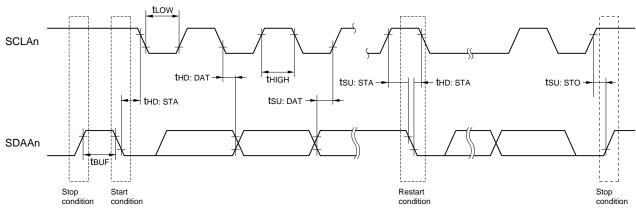

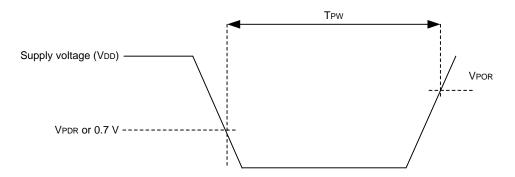

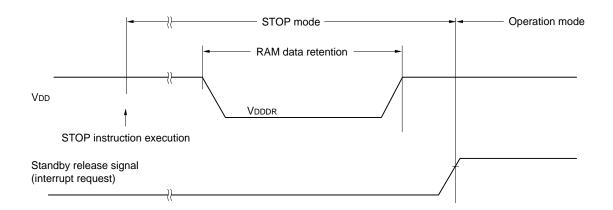

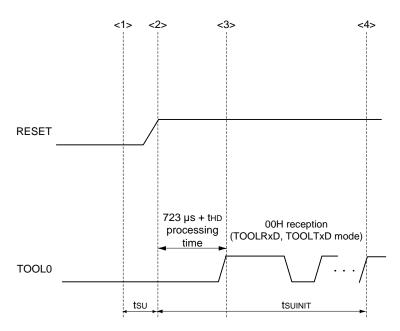

| High-speed on-chip oscillator clock frequency accuracy  |        | $-20C \le T_A \le 85C$ | -1.0 |      | +1.0 | %    |